密碼算法不運行也會有泄露

背景介紹

CMOS電路已經占據IC市場40余年,它可以持續占據市場這么久的一個重要的原因是它的閑置功耗比較低。當CMOS電路中的邏輯門不翻轉,即保持當前狀態的時候會有漏電流出現,此時CMOS門會產生靜態能量消耗。對于邏輯門來說不同的輸入產生的漏電流大小不同,會導致密碼運算的中間值與靜態能量消耗有關。

2021年,CHES會議上Thorben Moos和Amir Moradi討論了對靜態能量泄露的防護并利用PRESENT-80密碼算法進行實驗。目前常用的軟硬件密碼算法的防護方法有:HVT(高電壓閾值)、RSIS(隨機開始索引)、SDRL(平行雙軌邏輯)、QuadSeal(四對稱平行算法)和Threshold Implement(門限實現)。他們又提出了一種自己的方法用于防止靜態能量攻擊——ELB(邏輯消耗平衡)[1]。

不同防護方法介紹

低電壓閾值的邏輯門反轉速度比較快,所以經常用在比較重要的電路中,能量消耗較大。在對時間限制要求不高時,高電壓閾值的邏輯門可以被用在任何電路中,能量消耗較小。HVT就是利用能量消耗小導致的低信噪比來降低相關性來進行靜態能量防護。

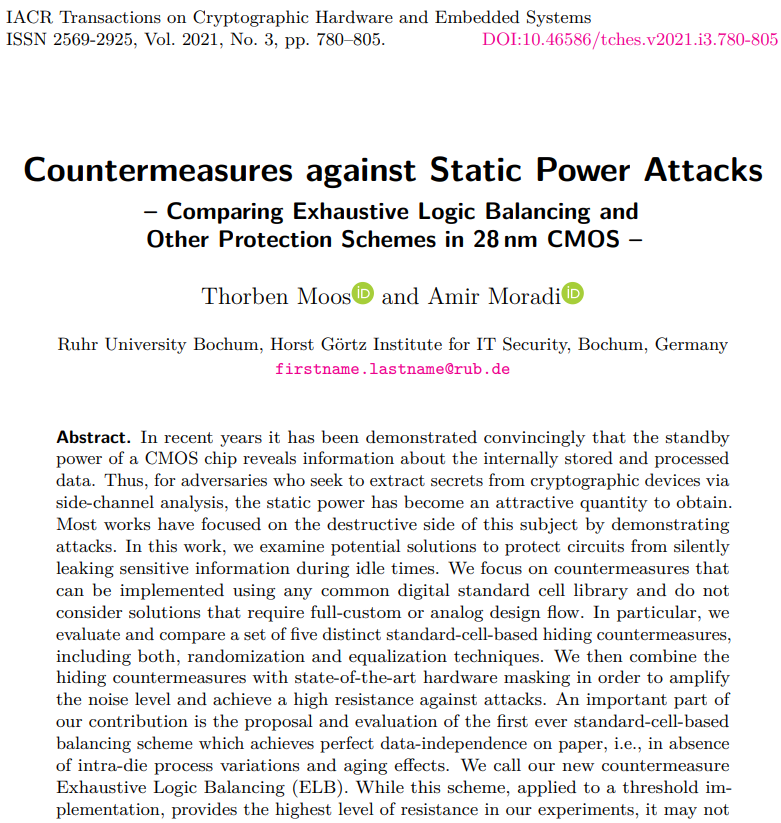

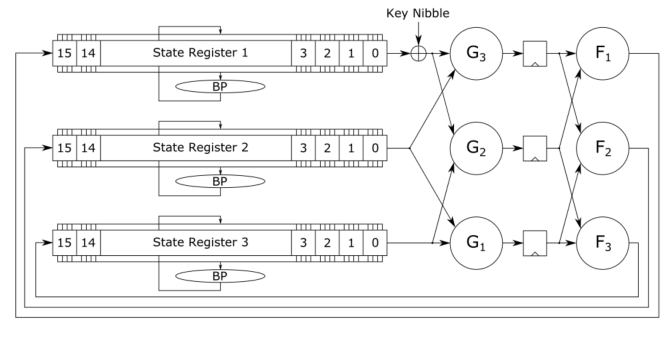

在側信道防御技術中,改變密碼算法的執行路徑是一個常用的方法,RSIS是隨機選擇16個S-box字節替換的起點。作者設計的硬件電路結構如圖1所示,正常的硬件電路比特置換部分接收輸入布線,而作者設計的電路需要先接收一個4比特的隨機開始的選擇邏輯電路,來決定哪些字節應該被反轉。

圖1. 加入RSIS防護的PRESENT-80硬件密碼電路實現方案

平衡能量消耗也是側信道防護技術中常用的手段,QuadSeal每次計算S(state⊕key)、S(state⊕key*)、S(state*⊕key)和S(state*⊕key*)(其中*運算為二進制表示下去反運算)來平衡漢明距離和漢明重量。這種方法可以很好的減少寄存器泄露,對于組合電路實現的密碼算法有一定的防護作用。

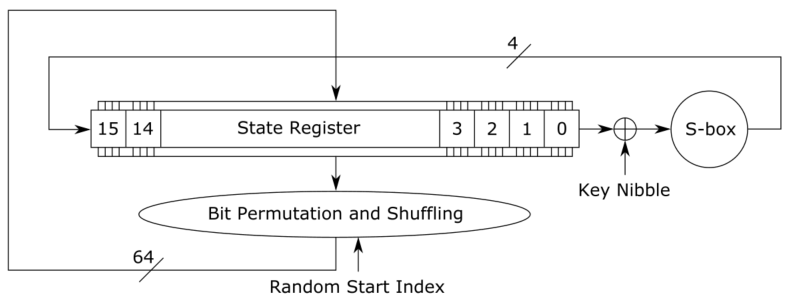

SDRL思想非常簡單,為了降低輸入向量和邏輯門之間的相關性,每個邏輯門都變成雙份,并且有著相反的邏輯輸入值,如下圖2所示。

圖2. 平行雙軌邏輯INV、NOR和D觸發器

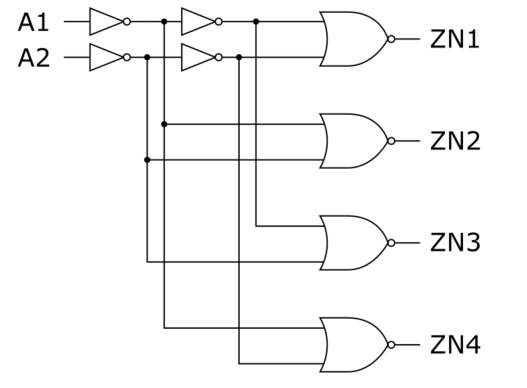

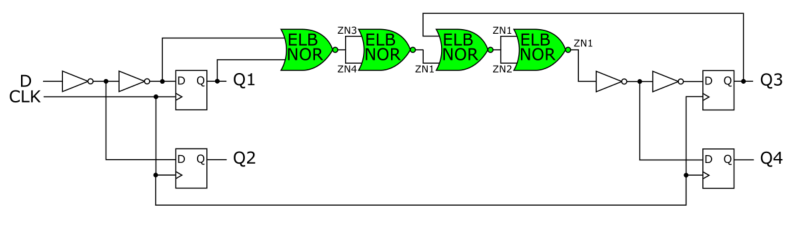

作者提出的ELB與SDRL想法相近,并且可以克服SDRL不能完全平衡泄露電流的問題。作者的想法是使得每一個門都能接收到所有可能的邏輯輸入,從而設計出能量平衡的邏輯門。在作者后續的實驗中,他們采用的邏輯門示例如圖3中的 NOR和圖4 中的D觸發器所示。

圖3. 功耗平衡NOR門

圖4. 利用ELB實現的NOR門組成的功耗平衡的D觸發器

在動態能量攻擊下,門限掩碼可以很好的防止高階泄露,并且對于靜態能量攻擊者也需要大量的觀測才能得到有用的信息。對于PRESENT-80的S-box的代數最高階為3,所以需要至少4 shares才能保證一階安全。如果直接這樣實現會導致芯片面積過大。所以論文作者把S-box分解成函數F和函數G,這兩個函數的代數階都是2,這樣只需要3 shares的門限實現,實現的架構如圖5所示。并且,門限掩碼方案可以和上面幾種保護措施一起實現。

圖5. 串行PRESENT-80的門限實現

實驗設置

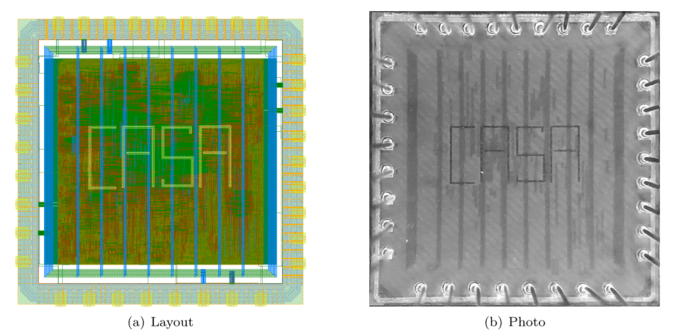

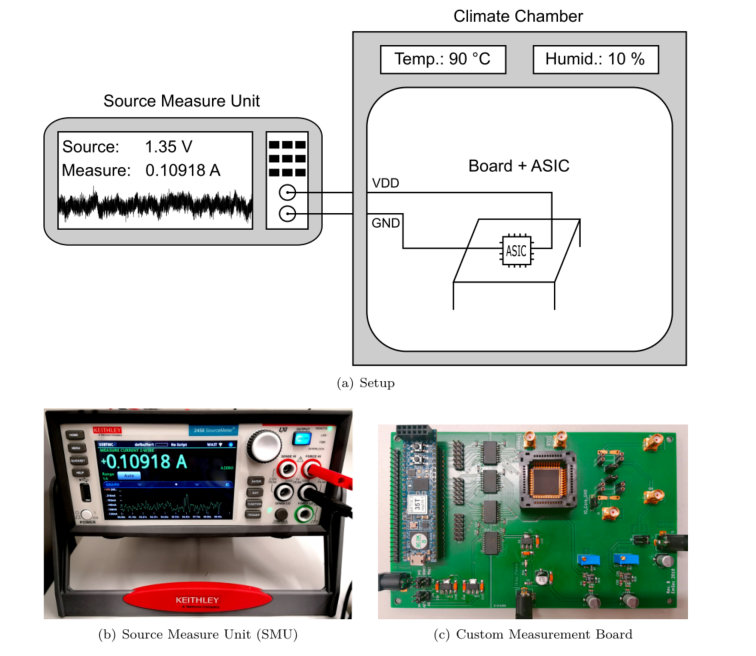

論文作者使用的密碼芯片如圖6所示,他們的實驗測量裝置如圖7所示。

圖6. 組合電路實現的ASIC原型

圖7. 實際實驗中的裝置

由于實驗中溫度會影響結果,所以他們利用一個溫控箱進行溫度的設置,具體設置如圖7(a)所示,圖7(b)可以測量電流大小并且可以給芯片供電,測量靜電流的步驟為:

①FPGA(圖7(c)板中最左邊的模塊)板子停止時鐘,讓PRESENT-80加密算法停止在第一輪,此時它產生一個觸發信號給SMU。

②SMU接收到觸發信號后等待20ms,在這20ms里測量電流,并將測量結果保存在內部緩存里,SMU睡眠等待下一次觸發。

③時鐘信號繼續,PRESENT-80算法結束運算。

實驗結果

論文作者采用的泄露分析方法是fixed vs fixed方法進行t-test,在20℃,0.9V下進行的泄露評估。其中HVT法效果最差,QuadSeal法和ELB法在卡方檢測中無泄露。但只有論文中提出里的ELB法在t檢驗和卡方檢驗中沒有泄露。由此,可以看出來他們設計的ELB組合電路可以有效地對抗靜態能量攻擊。

結論

目前大多數側信道攻防的研究人員關注重點都在動態能量泄露,而靜態能量也泄露著敏感的密碼運算的中間值,所以對于靜態能量的防護十分必要。常用的防護方法主要有加掩碼和平衡功耗兩種手段。作者通過分析和實驗對文中提到的幾種防護方法進行了評估,提出了一種基于能量消耗平衡的防護方法并結合門限掩碼大幅度降低泄露。

參考資料

[1] Moos, Thorben, and Amir Moradi. "Countermeasures against Static Power Attacks:–Comparing Exhaustive Logic Balancing and Other Protection Schemes in 28 nm CMOS–." IACR Transactions on Cryptographic Hardware and Embedded Systems (2021): 780-805.