一種比電磁能量分析還要遠的側信道分析方法

基于VITI的遠程能量分析

撰文 | 劉 錚

編輯 | 劉夢迪

背景介紹

FPGA(Field Programmable Gate Array),即現場可編程門陣列,可以根據用戶要求組合硬件資源以實現功能。隨著FPGA上可使用的資源越來越豐富,在一個FPGA上可以實現多個互相獨立的系統,這就為FPGA的安全性埋下了隱患,用戶可以在FPGA上實現惡意電路以監測FPGA的狀態,從而獲取在FPGA上運行的其它電路的信息。

2022年,CHES會議上Brian Udugama等人提出了一種名為VITI的FPGA片上傳感器,可以用于監測FPGA的能量變化,從而獲取同一FPGA上其它電路的側信息,以實現遠程能量攻擊。相比于已有的兩種片上傳感器,ring oscillators(ROs)和time to digital converters(TDCs),VITI具有消耗資源更少的特點。除此之外,他們還提出了一個全自動的自校準算法以及其輕量級電路實現,同時研究了參數對傳感器功效的影響[1]。

研究內容與方法

Remote Power Analysis(RPA),即遠程能量分析,指攻擊者通過在共享FPGA上實現自己的攻擊電路,來監聽目標電路的能量信息,從而竊取其密鑰信息的攻擊方法。其攻擊的原理圖如圖1所示。

圖1 RPA攻擊原理圖,攻擊者通過在共享FPGA上實現一個用于監測FPGA能量變化的攻擊電路,從而達到獲取目標電路能耗變化的目的

圖2是VITI的原理圖,其中IDELAYG和IDELAYC是兩個動態延時電路,其中IDELAYG的延時大小由CALIBRATION-FSM模塊調節,IDELAYC的延時大小固定。EN信號默認為1。電路通過每個時鐘周期采集A1A2A3...An的值作為FPGA的能量跡。

圖2 VITI原理圖,通過與門的延時變化來獲得FPGA的能耗變化

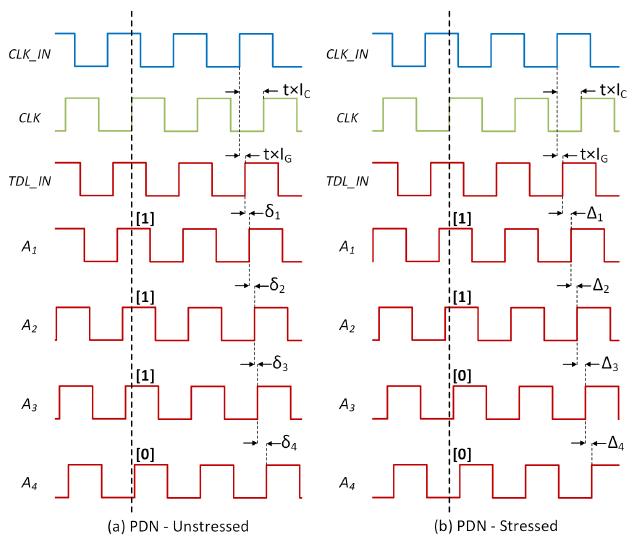

圖3是一個4比特VITI傳感器的時序圖,其中圖(a)是FPGA能量較高時的時序圖,圖(b)是FPGA能量較低時的時序圖,由于FPGA能量較高時與門的延時較低,FPGA能量較低時與門的延時較高,因此可以看到圖(a)中A1A2A3A4四個比特的值為1110,圖(b)中四個比特的值為1100,通過A3比特值的變化可以區分此時FPGA的能耗高低。

那么自然可以注意到,IDELAYG的延時大小是決定VITI是否有效的關鍵,為了確定IDELAYG的大小,論文提出了一個自適應算法,并實現為了CALIBRATION-FSM模塊,該算法可以簡述為:從小到大逐漸增大IDELAYG的延時大小,并反復進行實驗,直到某次實驗中A1A2A3A4發生變化為止,即可確定合適的IDELAYG延時大小。

圖3 4比特VITI時序圖,當FPGA能量較高時,與門的延時較低,反之與門的延時較高,與門延時的變化導致了兩種情況下A3比特值的變化

實驗結果與分析

論文進行了8個實驗以驗證VITI的效果并研究相關參數選擇的影響。其中實驗1到實驗6都是在SAKURA-G開發板上進行的實驗。SAKURA-G開發板上運行了一個128比特的AES。使用CPA攻擊第10輪的S盒。

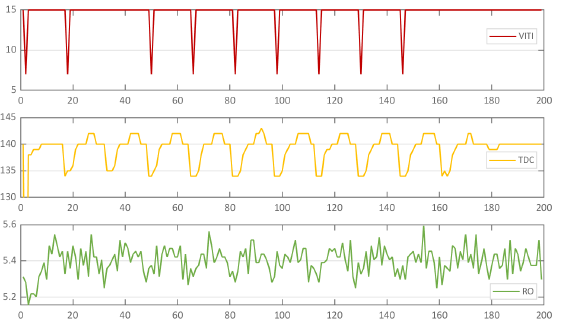

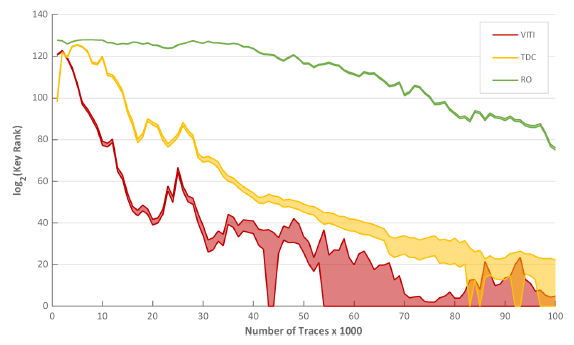

- VITI對比TDCs與ROs

圖4為VITI、TDC和RO采集到的能量跡,圖5為其對應的正確密鑰排名圖。可以看到,雖然VITI的精度是最低的,但VITI的攻擊效果卻是最好的,這說明VITI對泄露位置的判斷非常準確,噪聲較小。表1是VITI,TDC和RO的資源消耗表,可以看到,TDC的資源消耗是最小的。

圖4 VITI,TDCs和ROs采集的能量跡圖

圖5 VITI,TDC和RO的正確密鑰排名圖,其中橫坐標為攻擊使用的能量跡數量,縱坐標為正確密鑰排名對2取對數后的結果

表1 VITI、TDC及RO的資源消耗表

- VITI位置對實驗的影響

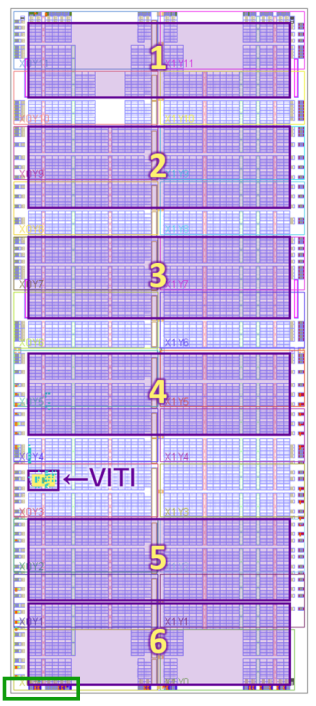

圖6(a)為VITI的位置分布,圖(b)為5個具有代表性的位置的正確密鑰排名圖。可以看到相似位置的VITI的效果也是相似的。論文由此得出結論,FPGA上的PDN分布并不均勻。

圖6 VITI位置分布圖,其中(a)為VITI的位置分布,(b)為5個具有代表性的位置的正確密鑰排名圖

- AES位置對實驗的影響

圖7為AES的位置分布圖,圖8為對應的正確密鑰排名圖。圖7中左下角為FPGA的時鐘輸入接口,可以看到當AES位于位置5和6時,時鐘信號會穿過AES模塊到達VITI,但是位置5和6的效果卻相差甚遠,由此可以看出,RPA攻擊能否成功與VITI的時鐘信號是否穿過AES模塊無關。同時論文得出結論,VITI和AES模塊的時鐘信號的布線與RPA攻擊的成功率無關,能量曲線上的波動不是來自于電線之間的相互影響,而是來自于FPGA自身的能量變化。

圖7 AES位置分布圖,其中左下角為FPGA的IO接口

圖8 不同AES位置的正確密鑰排名圖

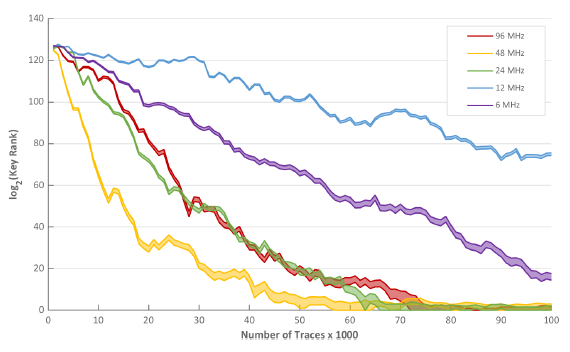

- AES頻率對實驗的影響

圖9為AES頻率變化實驗結果圖,其中VITI始終使用的是96MHz的頻率,通過修改AES的頻率來研究VITI頻率與AES頻率比值造成的影響。可以看到,除了12MHz以外,其它頻率使用RPA都成功了。論文猜測在12MHz下的電路執行了額外的優化導致攻擊不成功。即使VITI采樣頻率與AES頻率相同,RPA也能成功。說明SAKURA-G開發板的信噪比較高,一個點包含的信息量就足以成功進行攻擊。

圖9 AES頻率變化實驗結果圖

- VITI頻率、信噪比較高或較低對實驗結果的影響

論文在SAKURA-G上還做了三個實驗,由于實驗內容較為簡單在此簡述。第一個實驗固定AES頻率為6MHz,在6MHz到120MHz之間遍歷VITI的采樣頻率。實驗結果與實驗4相似,不做贅述。第二個實驗在FPGA上實現多個進行相同加密的AES模塊,用以模擬高信噪比的場景。第三個實驗在FPGA上實現多個執行不同加密的AES模塊,用以模擬噪聲較大的場景。不出意外地高信噪比成功執行CPA攻擊所需的能量跡條數更少,低信噪比所需的能量跡條數更多。

- 驗證VITI的可移植性

為了驗證VITI的可移植性,論文還進行了兩個實驗。第一個實驗使用了兩個Xilinx ML605開發板,每個開發板上都包含一個Xilinx Virtex-6 XC6VLX240T-1FFG1156 FPGA,兩個開發板燒錄進完全一樣的VITI電路。用以模擬在同一種芯片上同一種設計的可移植性。

第二個實驗將一個VITI和兩個AES上傳部署到了亞馬遜的Services Elastic Compute Cloud (AWS EC2) F1 instance上,盡管實驗只是用了FPGA上不到1%的資源,還是成功采集到100000條能量跡并執行了CPA攻擊。

總結與展望

這篇論文提出了一種相當輕量級的FPGA片上傳感器的設計與實現,并進行實驗驗證了設計的可行性與效率,相比于已有的片上傳感器,這篇論文提出的設計方案消耗的資源更少,采集到的能量跡執行CPA攻擊的效率更高。

參考資料

[1] Udugama, B., Jayasinghe, D., Saadat, H., Ignjatovi?, A., & Parameswaran, S. (2022). VITI: A Tiny Self-Calibrating Sensor for Power-Variation Measurement in FPGAs. IACR Trans. Cryptogr. Hardw. Embed. Syst., 2022, 657-678.